- cross-posted to:

- hardware@lemmy.world

- riscv

- cross-posted to:

- hardware@lemmy.world

- riscv

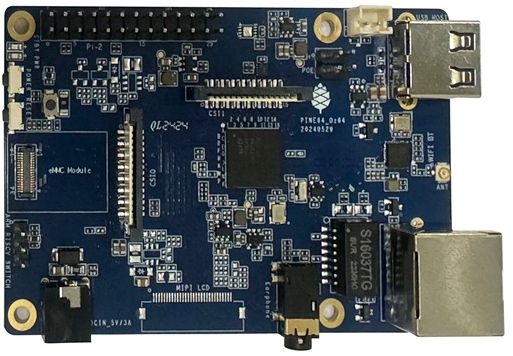

“I’d like a heterogeneous architecture sbc please”

They have played us for absolute fools.

The award for “WTF Design” goes to…

So you get either a mediocre ARM or a mediocre RISC-V, plus an even worse RISC-V, plus an 8051 core.

I’ve seen a lot of crazy, stupid SOC designs in the last decades, but this is extraordinary.

And the board has USB2, 10/100 Ethernet, Wifi and/or(?) BT, and 512MB RAM. With no real support on the software side, and to small to run a modern Linux efficiently. If this board costs more than $10, it is doomed.

Reminds me of my Commodore 128. You could boot it into 64 bit mode for legacy programs. I had exactly one C-128 game (which was a super complicated combat flight sim) so I only used it in C-64 mode.

I can think of one valid use case for this unsolved by any other solution:

Lets say a company has an SoC board base product currently currently base on ARM. They want to eventually migrate to RISC-V based solution.

If a company has a product currently written to use ARM compiled code, but wants to transition to RISC-V (which isn’t ready yet), they could deploy this board which could run today’s ARM implementation, and it would be future-ready when the RISC-V implementation would be released without having to replace hardware.

But why?

To experiment, I guess

Experiment how? What on earth could this possibly be useful for?

To learn about new architectures, now as they grow significance more and more, I’d say